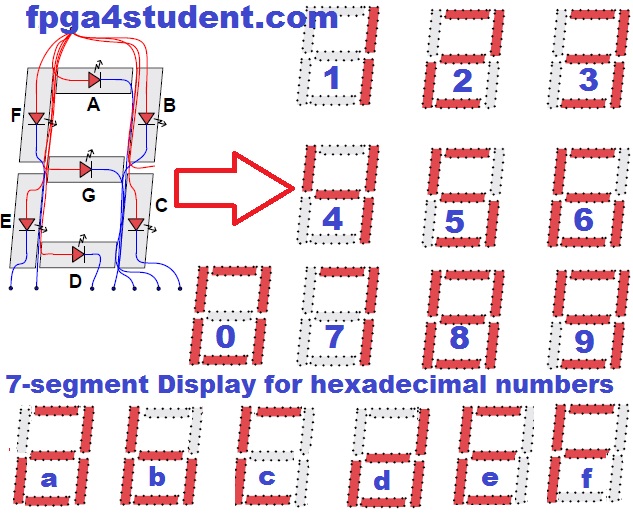

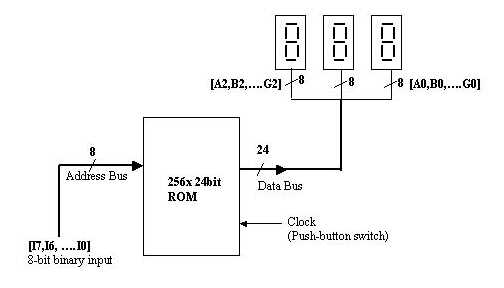

optimization of solution using algebraic equations in a reasonable time is not possible either. Therefore, an 8-bit binary to seven-segment decoder is a good candidate for a ROM based design.

7-Segment Display Driver for Multiple Digits (VHDL) - Logic - Electronic Component and Engineering Solution Forum - TechForum │ Digi-Key

7-Segment Display Driver for Multiple Digits (VHDL) - Logic - Electronic Component and Engineering Solution Forum - TechForum │ Digi-Key

![Quartus 2] Beginner Seven Segment Display help? Driving myself crazy : r/FPGA Quartus 2] Beginner Seven Segment Display help? Driving myself crazy : r/FPGA](https://i.imgur.com/5ua4BP0.jpg)